作者:Ryan Schnell,ADI公司应用工程师

为半桥配置的高端栅极供电起初似乎是一项棘手的任务,因为大部分系统都有较高的电平转换和驱动强度要求。本文论述让设计人员能够实现这一目标的可行解决方案。

简介

半桥拓扑广泛用于电源转换器和电机驱动器中。这在很大程度上是因为半桥可通过总线电压,为脉宽调制(PWM)信号提供高效同步控制。然而,在控制器和功率器件之间通常需要使用栅极驱动器,以获得更短的开关时间并出于安全性和/或功能性目的提供隔离。对于总线电压高于功率开关的栅极到源极电压最大限值的系统,必须采用不同于系统总线的电压驱动栅极。

本文讨论多种栅极驱动供电选项和基本设计制约因素,以及设计时的权衡取舍,帮助设计人员选择适当的拓扑。这些选项包括采用隔离式栅极驱动变压器、利用隔离式DC-DC馈送栅极驱动器为光电二极管或数字隔离器供电、自举配置,以及内置DC-DC电压源的隔离式栅极驱动器。对于功率较高的系统而言,功率开关器件占了BOM成本的很大一部分,且N型器件的导通电阻一般比尺寸和成本都相同的P型器件更低1。此外,若在半桥配置的单个引脚上使用两个相同的开关,则围绕时序要求而展开的设计(比如非交叠和死区时间)便可得到简化。由于这些原因,半桥配置通常由两个N型器件组成,这两个器件可以是NPN BJT、NMOS器件或N型IGBT。为简便起见,本文中的半桥配置采用两个NMOS器件,每引脚使用一个器件;这一概念同样适用于IGBT。为了使用BJT器件,设计时必须考虑到恒定的基极电流。

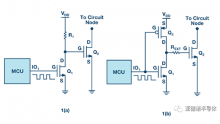

基本栅极驱动要求考虑图1中的典型半桥配置。两个MOSFET以互斥方式运行,因为如果两个MOSFET同时导通,则将产生直通。若要使MOSFET导通,则需VGS > VT,其中VGS是栅极到源极电压,而VT是特定MOSFET的阈值电压。工作时,建议MOSFET具有足够的过驱能力,因此在大部分应用中,实际栅极电压为VGS >> VT。在部分开关周期中,低端开关Q2导通而高端开关Q1断开。这表示VG1S1 < VT,且VG2S2 >> VT。在很多系统中,VG1S1等于0 V就足以保持高端开关断开。理想情况下,VOUT摆动到靠近系统地的位置。

忽略死区时间要求,则开关周期的其他部分为Q1导通而Q2断开,这意味着VG2S2 < VT且VG1S1 >> VT。在这段时间内,VOUT摆动至靠近总线电压的位置。注意,高端开关的源极连接至VOUT,表示栅极Q1在部分开关周期中,数值高于总线电压。

如果控制器IC直接连接至栅极Q1,则IC要求电压高于VBUS +VT,这在很多情况下都不现实。

栅极驱动器的一个主要作用是为功率开关提供快速开关时间,从而具备更快的上升和下降时间。这样可以降低功率级中与压摆率有关的损耗。过去,通过测量峰值电流来衡量驱动强度,或者更准确地说,是测量驱动器的RDSON。记住以下这点很重要:对于具备更高峰值电流(或更低RDSON)的栅极驱动器,其功率要求并不一定更高,因为开关栅极的功率通常由Q × V × FSW驱动,其中Q表示栅极电荷,V表示栅极电压摆幅,FSW表示系统的开关频率2。

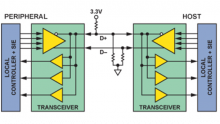

若要为高端开关的栅极驱动器供电,电源必须要能跟随VOUT电压,因为栅极以该电压为参考。适当去耦通常能解决隔离电源接地参考的快速变化而导致的任何电压尖峰问题。此外,每个不共享接地的栅极驱动器都可能需要自己的隔离电源。假设有一个典型的三相系统由三个半桥引脚组成,如图2所示。系统中有四个独立的接地参考,因为低端开关共享公共参考。取决于是否需要安全隔离或功能隔离,三相系统可以采用三个或四个专用电源。

任何项目需考虑的两个因素是解决方案的尺寸以及方案总成本。本文将通过不同的选项探讨权衡取舍。为栅极驱动器提供隔离电源的基本要求可以总结如下:

1) 提供足够的电压摆幅。

2) 部分开关周期的电压值高于总线电压。

3) 可跟随半桥中点电压的浮动接地。

4) 足够的驱动强度。

5) 紧凑的解决方案。

6) 合理的价格。

栅极驱动变压器

最早有一种提供隔离式栅极信号的解决方案使用栅极驱动变压器,比如图3中的系统。在该系统中,电能通过变压器传输,在副边形成所需的栅极电压。该系统的优势之一是其保证互补操作相对较为容易实现,方法是使其中一路副边输出极性与另一路相反。采用这种方式,若要驱动高端栅极至导通状态并驱动低端栅极至断开状态,可将电流以一个方向馈送至变压器的原边,相反方向的驱动电流则驱动栅极至相反状态。

由于在栅极驱动中,栅极驱动变压器用作电源,因此在靠近所驱动的栅极处,该解决方案的尺寸较小。器件数也较低,因为无需使用专用隔离式电源。变压器实际成本介于中等和昂贵之间。

变压器无法传输直流信号,因此在最基本的拓扑中,栅极在零点处达到伏秒平衡,这表示随着占空比上升,峰值正电压将下降3。这会对工作占空比造成限制,同时增加死区时间调谐的难度。占空比的快速变化还会产生磁芯饱和平衡问题。采用直流恢复拓扑时,需注意关断时很容易产生直通,因此栅极驱动变压器不太适合要求快速关断的应用,比如检测到系统故障时。必须复位栅极驱动变压器的磁芯,否则磁芯可能饱和,从而增加开关时序的设计难度。由于以上这些原因,目前在较高稳定性的高性能系统中很少采用栅极驱动变压器。

专用隔离电源

隔离栅极驱动的另一种方法,是使用隔离器传输时序信息。光耦合器利用光,跨越隔离栅将时序数据传输至光电晶体管或光电二极管。内部二极管的光输出量随着器件的老化和/或温度而下降,产生时序移位,因而死区时间需要更宽的裕量4。作为光耦合器的替代器件,数字隔离器一般通过感性耦合或容性耦合传输时序信息,从而有效避免了器件老化产生的时序移位,同时相比光耦合器可大幅降低温度产生的时序移位。采用光耦合器和数字隔离器时,输出缓冲器中的已传送信号确定栅极的最终驱动强度。该缓冲器可集成在隔离器封装内,也可部署在封装外。高压电平转换器使用上拉结构将时序数据传送至高端,可处理高达几百V的电压。如果半桥电压发生负振铃,则高压电平转换器可能会闩锁,而数字隔离器或光耦合隔离器不会产生这种情况。

为缓冲器供电的最直观的方法,是为半桥的每一个浮动区域提供专用的隔离式DC-DC转换器。对于多引脚系统,低端栅极驱动器可以共享一个电压源,只要有足够的电流输出即可,如图2中的系统示例所示。

专用隔离电源设置不存在占空比或最小开关频率要求,并且隔离式栅极驱动器的输入端可独立受控,允许调谐死区时间。但由于需使用额外的元器件,这种解决方案的代价是具有较大的尺寸和较高的成本。可利用反激式转换器或正向转换器等集成变压器的拓扑,在系统级创建一个隔离式电源。此外,还可采用单芯片模块,比如Recom提供的产品——这些产品针对隔离高电压设计5。

半桥自举配置

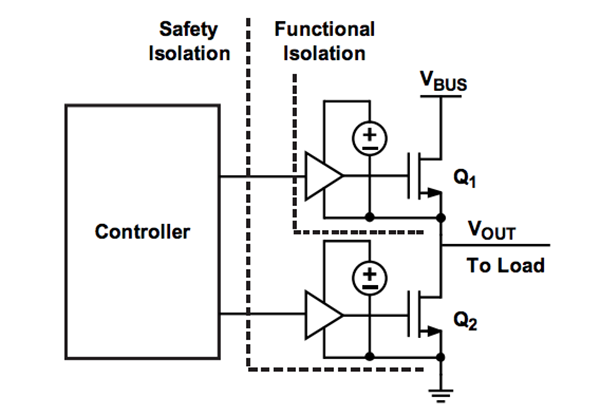

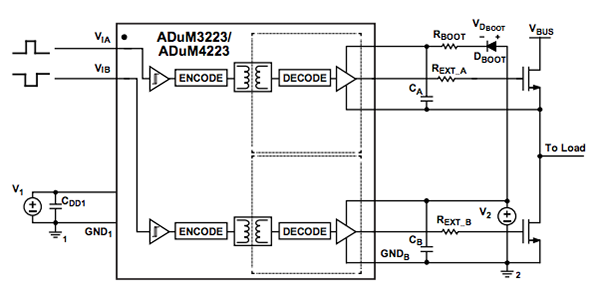

向上驱动栅极时,除了静态电流,隔离式栅极驱动器的输出端主要从供电轨获取电流。一旦IGBT或MOSFET的栅极电压到达供电轨,功耗便降为最低,因为栅极本质上是一个电容。对于高端驱动器而言,高端MOSFET导通时,该吸电流与半桥电压拉至总线电压的时间相吻合。这还意味着吸电流达到最大值前一刻,高端接地通过低端功率开关连接至低端接地。在高端供电轨上使用单个二极管以及数值适中的大电容后,便可提供临时电压源,如采用ADuM3223的图4所示。该图中,电阻与自举二极管串联,以便控制峰值充电电流6。

自举电容在低端开关导通期间充电并快速放电,以便填满栅极电容;但由于高端驱动器的静态电流,它在高端开关导通期间将缓慢放电。这会对系统占空比和开关频率产生限制作用7。只要有足够的时间来对自举电容充电,并且高端开关在超过电容所能支持的时间内未导通,则该解决方案的成本和尺寸优势便能凸显,特别是用于多相系统时。另外,在上电时可同时开启低端开关,从而一次充电多个自举电容。

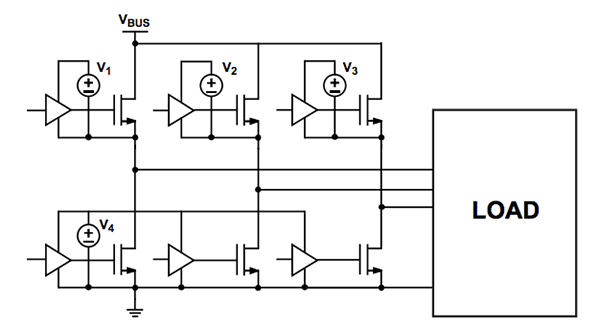

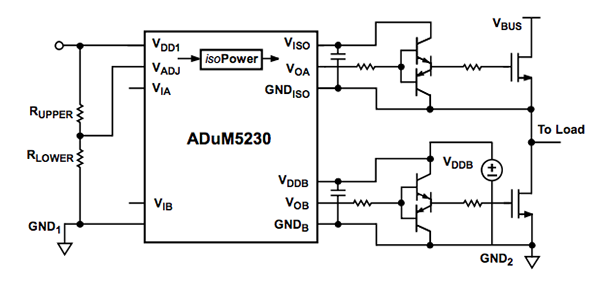

集成式电源和栅极驱动器

解决方案向更小尺寸的自然演化过程是创建集成隔离式电源和栅极驱动器功能的单片IC。传输隔离式电源的最高效方法是通过感性耦合。对于支持这样一个系统来说,光耦合器和容性耦合器所需的占位面积过大,工作速度过慢,并且功耗过高。对于完全集成式隔离电源和栅极驱动器拓扑电路而言,可在IC中部署小型芯片级电感。采用ADuM5230的这类系统如图5所示。该解决方案集成传输时序信息的变压器线圈,以及传输功率至高端驱动器的线圈,无需在高端使用额外的外部隔离式电源8。外部缓冲器可增加峰值电流输出,允许驱动更大的栅极电容。受限于效率,最大功耗(从而开关频率和/或最大栅极电荷负载)也受到限制。随着技术进步,满足更高系统要求的单芯片解决方案将会应运而生。

撇开功耗方面的限制,该集成式隔离电源和栅极驱动器系统具有出色的解决方案尺寸,同时移除了占空比和最低开关频率的限制。

小结

为半桥配置的隔离端供电存在一定难度,但有很多拓扑可供设计人员选择。栅极驱动变压器在器件数方面占有优势,但受限于驱动信号的复杂程度,而且磁芯的动态特性对其也有限制作用。专用隔离电源使占空比和频率要求不复存在,但缺点是成本较高、解决方案尺寸较大。如果可以限制占空比和开关频率,则半桥自举配置便是一个高性价比选择,可大幅减少器件数,降低解决方案成本。目前已出现高度集成的解决方案,这类解决方案利用内部变压器完成功率传输,节省了尺寸,减少了器件数。有了如此众多的拓扑,设计人员便拥有创建鲁棒半桥解决方案的工具。

作者简介

Ryan Schnell是ADI公司的应用工程师。 他的工作涉及使用iCoupler®技术来实现隔离的隔离式栅极驱动器,以及各种电源管理产品。他拥有科罗拉多大学电气工程学士/硕士学位,以及电源电子学博士学位。

参考文献

1. Hu, Calvin. “Modern Semiconductor Devices forIntegrated Circuits.” Prentice Hall; 2009

2. Concept, “IGBT and MOSFET Drivers CorrectlyCalculated”, application note AN-1001, pp. 1.

3. Ridley, Ray. “Gate Drive Design Tips,” Power SystemsDesign Europe, 2006, pp. 14-18.

4. Foo, Jye Chwan. “Gauging LED Lifetime inOptocouplers”, Machine Design, Sep 20, 2012.

5. Recom, “ECONOLINE DC/DC-Converter,” RP Seriesdata sheet, Rev. 0, 2014.

6. Analog Devices, Inc., “ADuM3223”, data sheet, Rev. D,http://www.analog.com/en/interface-isolation/digitalisolators/adum3223/p....

7. Adams, Jonathan. “Bootstrap Component Selection forControl ICs”, International Rectier, Design Tip DT98-2.

8. Analog Devices, Inc., “ADuM5230”, data sheet, Rev. B, http://www.analog.com/en/interface-isolation/digitalisolators/adum5230/p..., 2013.