电路功能与优势

低压差分信号(LVDS)是低功耗、高速、点对点通信的既定标准(TIA/EIA-644)。它用于在仪器仪表和控制应用中通过背板或短电缆链路传输大量数据,或分配高速时钟至应用电路的不同部分。

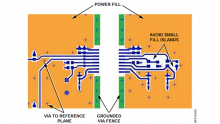

图1所示电路表示LVDS接口的隔离。隔离LVDS接口的好处有:保护器件免受故障影响(安全隔离),以及增加鲁棒性(功能隔离)。

ADuM3442为ADN4663 LVDS驱动器的逻辑输入以及ADN4664 LVDS驱动器的逻辑输出提供数字隔离。除了使用ADuM5000提供隔离式电源,在工业和仪器仪表应用中隔离LVDS链路还面临着许多挑战,包括:

• 逻辑信号与LVDS驱动器/接收器隔离、确保电路总线端的标准LVDS通信。

• 高度集成的隔离仅使用两个额外的宽体SOIC器件(ADuM3442和 ADuM5000)来隔离标准 LVDS器 件(ADN4663和ADN4664)。

• 与传统隔离(光耦合器)相比功耗更低。LVDS应用的特性之一是低功耗工作。

• 多通道隔离。LVDS应用中,使用并行通道以尽量增大数据吞吐量。本电路演示4通道隔离(本实例中采用两条发射通道和两条接收通道)。

• 工作速度高;最高工作速度达150 Mbps,轻松满足基本LVDS的速度要求。

详文请阅:隔离式LVDS接口电路