作者:Jonathan Harris,ADI公司应用工程师

简介

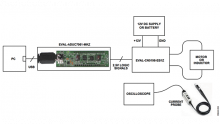

随着高速ADC跨入GSPS范围,与FPGA(定制ASIC)进行数据传输的首选接口协议是JESD204B。为了捕捉频率范围更高的RF频谱,需要宽带RF ADC。在其推动下,对于能够捕捉更宽带宽并支持配置更灵活的SDR(软件定义无线电)平台的GSPS ADC,高速串行接口(在此情况下即JESD204B)是必不可少的。JESD204B标准是一种分层规范,了解这一点很重要。规范中的各层都有自己的功能要完成。应用层支持JESD204B链路的配置和数据映射。传输层实现转换样本与成帧未加扰八位字之间的映射。加扰层可以选择性地获取八位字并进行加扰或解扰,以便通过延展频谱尖峰来降低EMI效应。加扰在发送器中完成,解扰在接收器中完成。在数据链路层中,可选加扰的八位字编码成10位字符。该层也是产生或检测控制字符的地方,目的是监视和维护通道对齐。物理层即串行器/解串器(SERDES)层,负

责以线路速率发送或接收字符。该层包括串行器、驱动器、接收器、时钟和数据恢复电路。图1显示了这些层在JESD204B中的安排。为了更好地理解该规范,详细阐释各层对了解ADC样本如何映射到8B/10B串行字是有好处的。