摘要

按照许多年前老师的教导,我们会在运算放大器的两个输入端放上相等的阻抗。本文探究为什么会有这么一条经验法则,以及我们是否应当遵循这种做法。

老师的教导

如果您是在741运算放大器1横行天下的时代长大的,那么平衡运算放大器输入端电阻的观念必定已扎根在您的脑海中。随着时间的流逝,由于不同电路技术和不同IC工艺的出现,这样做可能不再是对的。事实上,它可能引起更大直流误差和更多噪声,使电路更不稳定。我们以前为什么要那样做?什么变化导致我们现在这样做可能是错误的?

在二十世纪六十年代和七十年代,第一代运算放大器采用普通双极性工艺制造。为了获得合理的速度,差分对尾电流一般在10 µA到20 µA范围内。

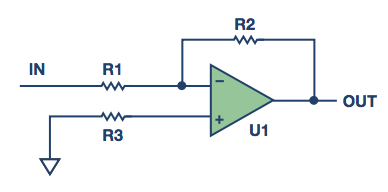

而β值为40到70,故输入偏置电流在1 μA左右。然而,晶体管匹配度并不那么高,所以输入偏置电流不相等,导致输入偏置电流之间有10%到20%的偏差(称为“输入失调电流”)。在同相接地输入端增加一个与输入电阻R1和反馈电阻R2的并联组合相等的电阻(图1中的R3),可以让阻抗相等。通过一些计算可以证明,误差降至Ioffset × Rfeedback。由于Ioffset为Ibias的10%到20%,这将有助于降低输出失调误差。

直流误差

为降低双极性运算放大器的输入偏置电流,许多运算放大器设计集成了输入偏置电流消除功能。OP07就是一个例子。输入偏置电流消除功能的增加2使偏置电流大大降低,但输入失调电流可能为剩余偏置电流的50%到100%,所以增加电阻的作用非常有限。某些情况下,增加电阻反而可能导致输出误差提高。

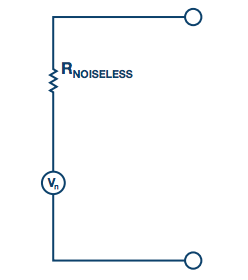

噪声

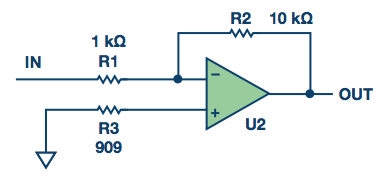

电阻热噪声的计算公式为√4kTRB,故1 kΩ电阻会有4 nV/√Hz的噪声。增加电阻会增加噪声。图2中,出人意料的是,虽然909 Ω补偿电阻是值最低的电阻,但由于从该节点到输出端的噪声增益,它给图2输出端贡献的噪声最多。R1引起的输出噪声为40 nV/√Hz,R2为12.6 nV/√Hz,R3为42 nV/√Hz。因此,请勿使用电阻。另一方面,如果运算放大器采用双电源供电,并且一个电源先于另一个电源上电,那么ESD网络可能发生闩锁问题。这种情况下,可能希望增加一定的电阻来保护器件。但若使用的话,应在电阻上放置一个旁路电容以减少电阻的噪声贡献。

稳定性

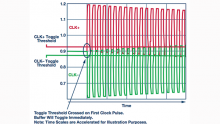

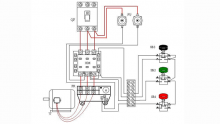

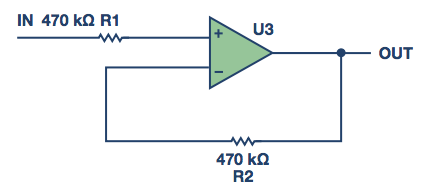

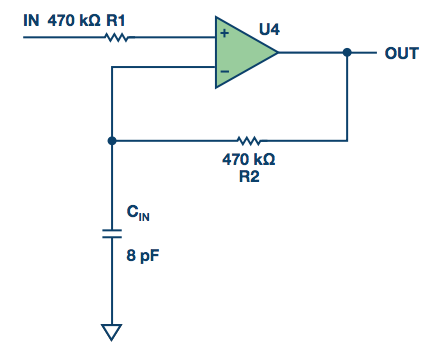

所有运算放大器都有一定的输入电容,包括差模和共模。如果运算放大器连接为跟随器,并且在反馈路径中放入一个电阻以平衡阻抗,那么系统可能容易发生振荡。原因是:大反馈电阻、运算放大器的输入电容和PC板上的杂散电容会形成一个RC低通滤波器(LPF)。此滤波器会引起相移,并降低闭环系统的相位裕量。如果降低得太多,运算放大器就会振荡。一位客户在一个1 Hz Sallen-Key低通滤波器电路中使用AD8628 CMOS运算放大器。由于转折频率较低,电阻和电容相当大(参见图3)。输入电阻为470 kΩ,所以客户在反馈路径中放入一个470 kΩ电阻。此电阻与8 pF的输入电容(参见图4)一起提供一个42 kHz的极点。AD8628的增益带宽积为2 MHz,因此它在42 kHz仍有大量增益,并发生了轨到轨振荡。把470 kΩ电阻换成0 Ω跳线即解决了问题。因此,反馈路径中应避免使用大电阻。这里,何者为大取决于运算放大器的增益带宽。对于高频运算放大器,例如增益带宽积超过400 MHz的

ADA4817-1,1 kΩ反馈电阻就称得上是大电阻。务必阅读数据手册以了解其中的建议。

结语

多年来的实践会产生一些有用的经验法则。审核设计时,最好仔细检视这些经验法则,判定它们是否仍然适用。关于是否需要增加平衡电阻,如果是带有输入偏置电流消除功能的CMOS、JFET或双极型运算放大器,那么可能不需要增加。

读完本文后,您可能会意外提问是关于噪声的。请回答以下三个问题:

问题1:以下哪个噪声是在电阻中产生的?

• 爆米花噪声

• 红噪声

• 粉红噪声

• 1/f噪声

• 白噪声

• 约翰逊噪声

• 奈奎斯特噪声

• 白噪声

问题2:室温(20°C)条件下,等效噪声带宽为20 kHz时,10 kΩ电阻产生的均方根噪声是多少?

问题3:24位音频ADC的输入电压范围为2.5 V时,用此VNOISE可以获得多少闪烁位?

作者简介:Harry Holt [harry.holt@analog.com]是ADI公司的资深应用工程师。过去四年在核心应用部门工作,此前六年在精密放大器部门工作。之前他曾在美国国家半导体公司工作了28年,从事各种产品的现场和工厂应用工作,包括数据转换器、运算放大器、基准源、音频编解码器和FPGA。他拥有圣何塞州立大学电气工程学士学位(BSEE),并且是国家工程荣誉协会(Tau Beta Pi)终身会员和IEEE高级终身会员。