使用 时钟分配器件1 或者扇出缓冲器为ADC 和DAC 提供时钟时,需要考虑印刷电路板上的走线和输出端接,这是信号衰减的两个主要来源。

时钟走线与信号摆幅

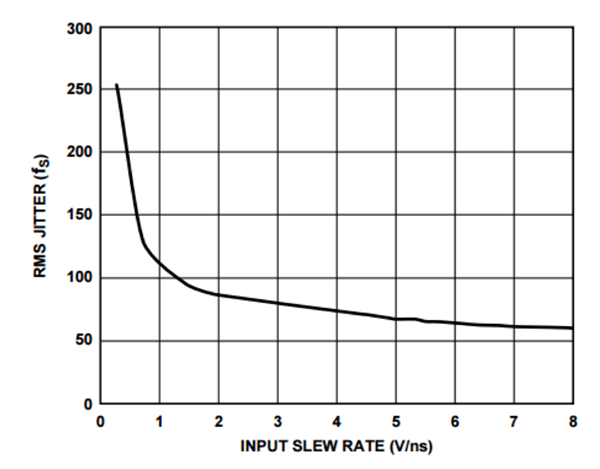

PCB 上的走线类似于低通滤波器,当时钟信号沿着走线传输时,会造成时钟信号衰减,并且脉冲沿的失真随线长增加。更高的时钟信号频率会导致衰减、失真和噪声增加,但不会增加抖动,在低压摆率时抖动最大(图 1),一般使用高压摆率的时钟沿。为了实现高质量的时钟,要使用高摆幅时钟信号和短时钟 PCB 走线;由时钟驱动的器件应该尽可能靠近时钟分配器件放置。

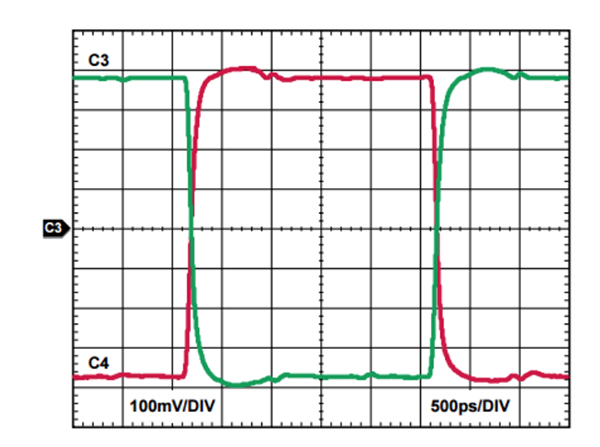

ADCLK9542 时钟扇出缓冲器和 ADCLK9143 超快时钟缓冲器就是两款此类时钟分配器件。ADCLK954 包括 12 个输出驱动,可以在 50-Ω的负载上驱动全摆幅为 800-mV 的 ECL(发射极耦合逻辑)或者 LVPECL(低压正 ECL)信号,形成 1.6 V 的总差分输出摆幅,如图2 所示。它可以在4.8 GHz 反转率下工作。ADCLK914 可以在 50-Ω负载上驱动 1.9 V 高压差分信号 (HVDS),形成 3.8 V 的总差分输出摆幅。ADCLK914 具有7.5-GHz 的反转率。

当驱动 DAC 时,时钟分配器件应该尽可能靠近 DAC 的时钟输入放置,这样,所需的高压摆率、高幅度时钟信号才不会引起布线困难、产生 EMI 或由电介质和其它损耗造成减弱。值得注意的是,走线的特性阻抗(Z0)会随走线尺寸(长度、宽度和深度)而变化;驱动器的输出阻抗必须与特性阻抗匹配。

输出端接

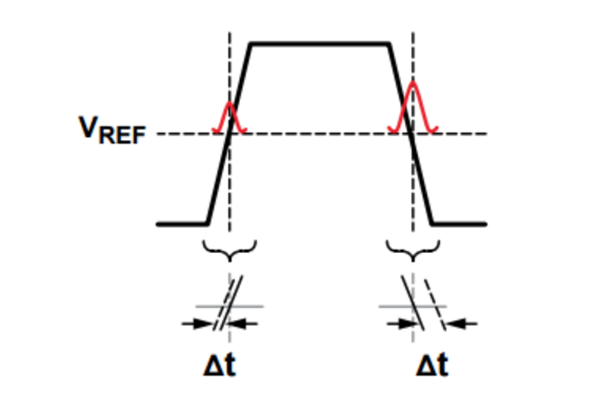

时钟信号衰减会增加抖动,因此对驱动器输出的端接很重要,这可以避免信号反射,并可通过相对较大的带宽实现最大能量传输。确实,反射可以造成下冲和过冲,严重降低信号和整体时钟的性能,或者在极端情况下,可能会损坏接收器或驱动器。反射因阻抗不匹配而引起,在走线没有适当端接时发生。由于反射系数本身具有高通特性,因此这对具有快速上升和下降时间的高速信号更重要。反射脉冲与主时钟信号相叠加,削弱了时钟脉冲。如图3 所示,它对上升沿和下降沿增加了不确定的延时或者抖动,从而影响时钟信号的边沿。

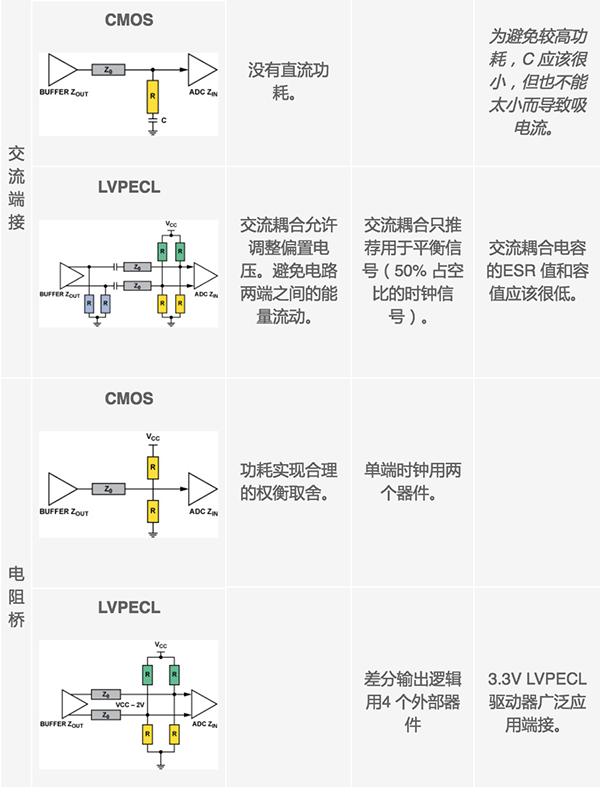

端接不当使回声的幅度随着时间而变化,因此∆t 也会随时间变化。端接的时间常数也会影响回声脉冲的形状和宽度。基于以上原因,反射引起的附加抖动,从形状看类似增加经典抖动的高斯特性。为了避免抖动和时钟质量降低的不利影响,需要使用表 1 中总结的恰当信号端接方法。Z0 是传输线的阻抗; ZOUT 是驱动器的输出阻抗, ZIN 是接收器的输入阻抗。显示CMOS 和 PECL/LVPECL电路。

表1. 时钟端接

参考电路

1www.analog.com/en/products/clock-and-timing/clock-generation-distributio....

2www.analog.com/en/clock-and-timing/clock-generation-and-distribution/adc....

3www.analog.com/en/clock-and-timing/clock-generation-and-distribution/adc....

作者:Jerome Patoux

Jerome Patoux is a product marketing engineer for ADI's Clock and Signal Synthesis Group in Greensboro, NC. In 2002, he graduated from ESIGETEL, Avon, France, with a master's degree in electronics and telecommunications engineering. He also has a master's degree in international project management from the University of Quebec in Hull-Gatineau, Canada, and ISMANS, Le Mans, France. Prior to joining ADI in 2005, Jerome worked as a radio engineer for SFR Group and as a department manager for SNCF.