作者:Stuart Servis和Miguel Usach Merino

简介

您有没有检查过网络上有多少条关于“ADC缓冲器设计”的内容?答案是超过400万条,在如此多的参考文献中很难找到我们需要的内容。对于大多数模拟和混合信号数据采集系统设计工程师来说,这可能不是很意外,因为设计无缓冲模数转换器(ADC)的外部前端需要有耐心和大量建议。它常常被视为一种艺术形式,是经过多年摸索掌握其窍门的古怪大师的保留地。对于没有经验的人来说,这是一个令人沮丧的反复尝试过程。大多数时候,由于相互关联的规格要求很多,迫使设计人员不得不进行很多权衡(和评估)才能达到最佳效果。

挑战

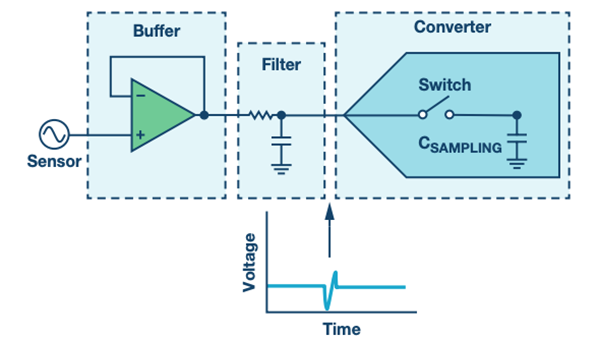

放大器级的设计由两个彼此相关的不同级组成,因此问题变得难以在数学上建模,特别是因为有非线性因素与这两级相关。第一步是选择用来缓冲传感器输出并驱动ADC输入的放大器。第二步是设计一个低通滤波器以降低输入带宽,从而最大限度地减少带外噪声。理想的放大器是提供刚刚好的带宽以正确缓冲传感器或变送器产生的信号,而不会增加额外噪声,并且功耗为零,但实际放大器与此相距甚远。在大多数情况下,放大器规格将决定整体系统性能,尤其是在噪声、失真和功耗方面。为了更好地弄清楚问题,第一步是了解离散时间ADC的工作原理。

离散时间ADC获得连续时间模拟信号的样本,然后将其转换为数字码。当信号被采样时,根据模拟转换器的类型,同一固有问题有两种不同的情况。

SAR ADC集成一个采样保持器,其基本上由一个开关和一个电容组成,作用是保持模拟信号直到转换完成,如图1所示。