ADC架构I:Flash转换器

selina -- 周三, 03/14/2018 - 14:26

作者:Walt Kester

简介

作者:Walt Kester

简介

简介

作者 :Walt Kester

简介

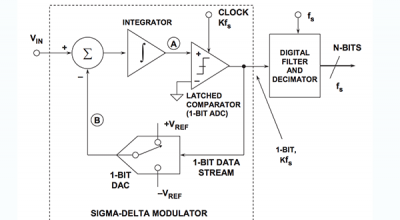

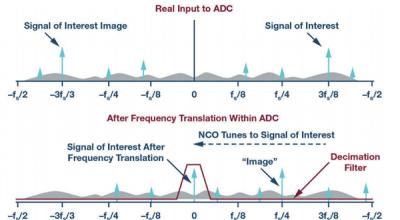

教程 MT-022 已论述了 Σ-Δ 型 ADC 的基本原理。本教程将介绍一些更高级的概念,包括空闲音、多位 Σ-Δ、MASH、带通 Σ-Δ,并提出一些示例应用。

空闲音考量

时间交错技术可使用多个相同的 ADC(文中虽然仅讨论了 ADC,但所有原理同样适用于 DAC 的时间交错特性),并以比每一个单独数据转换器工作采样速率更高的速率来处理常规采样数据序列。简单说来,时间交错(IL)由时间多路复用 M 个相同的 ADC 并联阵列组成。

Mark Thoren - 科学专家 - 混合信号

Andrew Thomas - 设计工程师

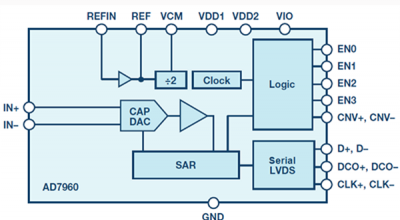

许多采用一个精准模数转换器进行信号数字化处理的系统都需要在信号源和 ADC 之间布设某种信号调理电路。除了它的其他功能之外,该电路还必须准确地驱动 ADC 的输入。由于同时需要高性能和高速度以处理 ADC 输入电流,因而会提出一项实质性的额外设计挑战。

摘要

Ian Beavers ADI公司

设计中选择高分辨率ADC时,经常需要了解一些数据手册中通常可能不会公布的特性数据,例如,全部代码范围内的转换器噪声性能。在数据手册中,您不一定能找到这一规格。

幸运的是,现在有一款工具可以分析ADC的这些数据以及其他参数,并从系统角度出发评估转换器的真正性能。

作为应用工程师,我们经常遇到各种有关差分输入型高速模数转换器(ADC)的驱动问题。事实上,选择正确的ADC驱动器和配置极具挑 战性。为了使鲁棒性ADC电路设计多少容易些,我们汇编了一套通用"路障"及解决方案。本文假设实际驱动ADC的电路—也被称为ADC 驱动器或差分放大器 — 能够处理高速信号。

引言