采用高速模数转换器(ADC)的系统设计非常困难,对于输入有两类ADC架构可供选择:缓冲型和无缓冲型。

缓冲和无缓冲架构的特征

缓冲架构的基本特征

* 高线性度缓冲器,但需要更高的功率;

* 更易设计输入网络与高阻抗缓冲器接口,因为它提供固定的输入端接电阻;

* 缓冲器提供采样电容与输入网络之间的隔离,电荷注入瞬变更小。

无缓冲架构的基本特征

* 输入阻抗由开关电容设计设置;

* 功耗较低;

* 输入阻抗随时间变化(采样时钟-采样保持器);

* 来自采样电容的电荷注入反射回输入网络。

无缓冲ADC

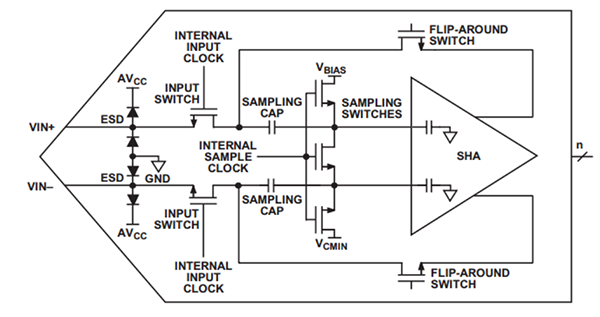

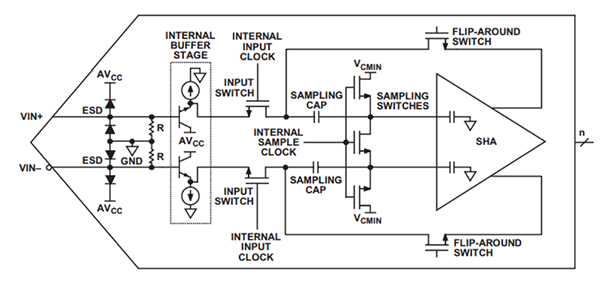

开关电容ADC(见图1)就是一类无缓冲ADC。无缓冲ADC的功耗通常远低于缓冲ADC,因为前者的外部前端设计直接连到ADC的内部采样保持(SHA)网络。

这种方法有两个缺点

输入阻抗随着时间和模式而变化;

第二是电荷注入会反射回ADC的模拟输入端,可能导致滤波器建立问题。

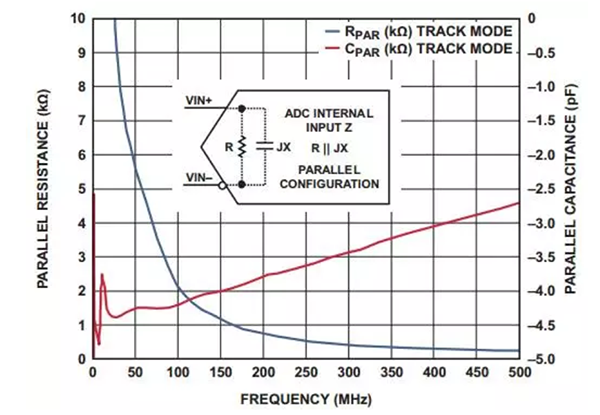

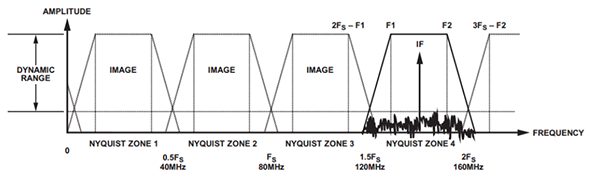

当模拟输入频率改变,以及SHA从采样模式变为保持模式时,无缓冲ADC的输入阻抗也会变化。必须使输入与ADC采样模式匹配,如图2所示。

在基带范围的较低频率时,输入阻抗的实部(蓝线)在数千欧范围内,在200 MHz以上时则滚降到2 kΩ。输入阻抗的虚部或容性部分(红线)也是如此,低频时的容性负载相当高,高频时逐渐变小到2 pF。这使得输入结构的设计更加困难,特别是当频率高于100 MHz时。

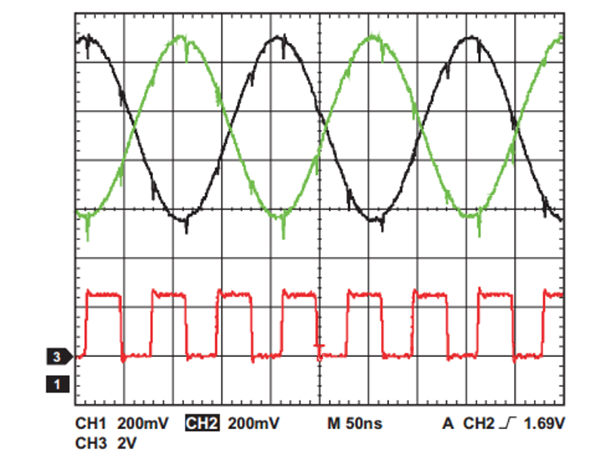

ADC如何能采样一个坏信号(如图3所示)并实现良好的性能?

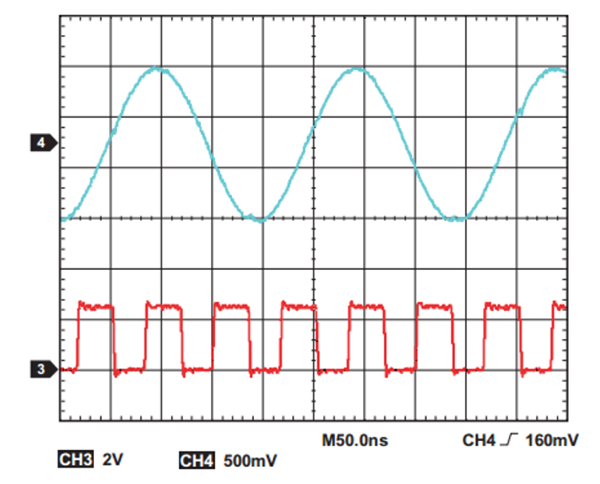

查看图4所示的差分ADC输入,输入信号干净得多。坏信号毛刺已消失。共模抑制是差分信号的固有特性,它能消除任何噪声,无论是来自电源、数字注入还是电荷注入。查看无缓冲ADC毛刺的另一种方法是在时域中,利用频谱分析仪测量返回模拟输入的噪声。下图显示了开关电容ADC结构对模拟输入的影响。

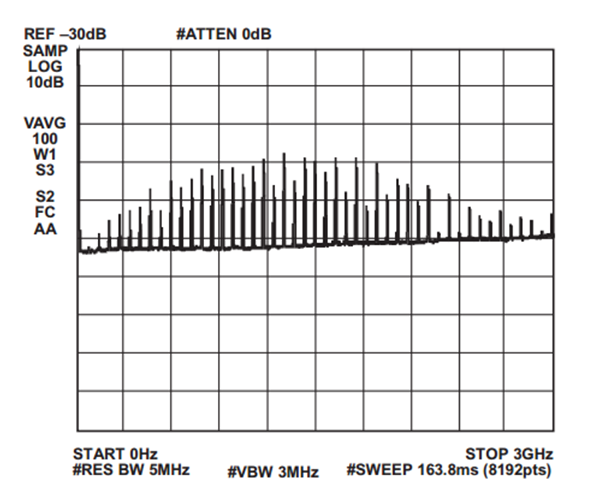

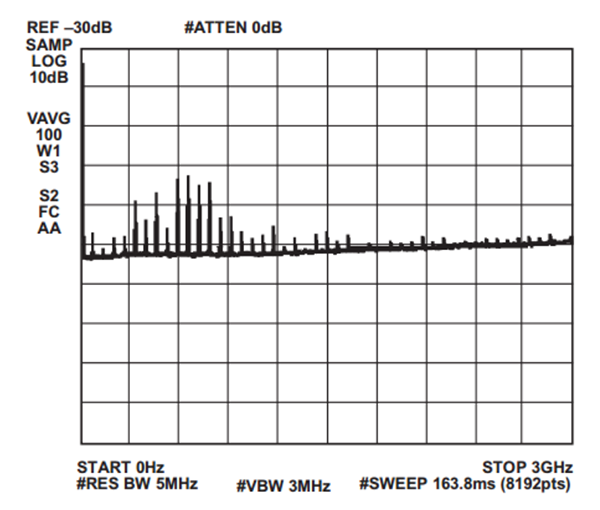

图5显示时钟的谐波、噪声和其它杂散成分在3 GHz以上的频谱中馈通。匹配ADC输入以降低时钟馈通一般可将大部分谐波抑制10dB 以上。

图6中,通过在模拟输入的每一侧串联一个低Q电感或铁氧体磁珠,实现了输入匹配。这是降低进入模拟输入端的噪声量的一种方法,需要时可采用。

缓冲ADC

缓冲输入ADC(见图7)更易于使用,因为输入阻抗是固定值。隔离缓冲器抑制了电荷注入尖峰,因而开关瞬变显著降低。缓冲器由内部双极结晶体管级组成,具有固定的输入端接电阻。

与开关电容ADC不同,此端接电阻不随模拟输入频率而变化,因此驱动电路的选择得以简化。缓冲输入级的缺点是ADC的功耗较高。然而,由于它经过专门设计,具有非常好的线性度和低噪声特性,因此在ADC的全部额定带宽内,输入阻抗都是恒定的。

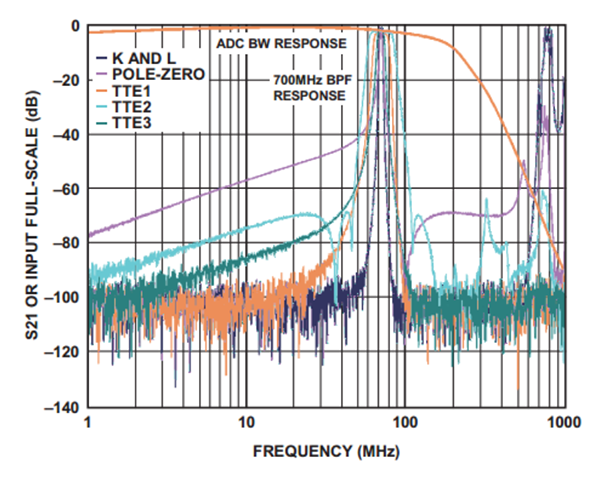

设计抗混叠滤波器(AAF)时应当注意,过多的元件可能会导致容差不匹配,进而产生偶数阶失真。电感并非特性相同,不同电感的响应可能大不相同。廉价、低质量的电感一般表现不佳。此外,有时很难在电感上实现良好的焊接连接,这就会引起失真。务必将AAF的阻带区间规定为平坦的,因为宽带噪声仍有可能折回带内(见图8)。

多数转换器具有很宽的模拟输入带宽。如果不使用AAF,混叠会降低动态范围。AAF应按照等于或略大于目标信号带宽的要求进行设计。滤波器的阶数和类型取决于所需的阻带抑制和通带纹波。AAF在ADC的整个带宽内应具有充分的阻带抑制性能。

图9说明了阻带抑制在AAF设计中的重要性。注意,转换器带宽(红色曲线所示)远大于要采样的频带。因此,噪声和杂散可能会折回要采样的带内频率中。注意淡蓝曲线和粉红曲线,其中滤波器响应出现在阻带抑制区间。还应注意深绿或橙色曲线,阻带抑制保持恒定。