作者:Ian Beavers,ADI公司应用工程师

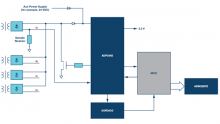

JESD204B串行数据链路接口针对支持更高速转换器不断增长的带宽需求而开发。作为第三代标准,它提供更高的通道速率最大值(每通道高达12.5 Gbps),支持确定延迟和谐波帧时钟。此外,得益于转换器性能的提升——这些转换器兼容开放市场FPGA解决方案,并且可扩展——现已能轻松传输大量待处理的数据。

FPGA供应商已讨论了许多年有关千兆串行/解串(SERDES)接口的话题,虽然过去大部分模数转换器(ADC)和数模转换器(DAC)并未配备这类高速串行接口。FPGA和转换器不与任何通用标准接口,无法利用SERDES的高带宽。JESD204B兼容型转换器能够解决这个问题,而人们针对这种新功能提出了一些问题。

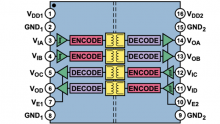

什么是8b/10b编码,为什么JESD204B接口需使用这种编码?

无法确保差分通道上的直流平衡信号不受随机非编码串行数据干扰,因为很有可能会传输大量相反的1或0数据。通过串行链路传输的随机数据还可能长时间无活动状态,并在相对较长的时间内为全1或全0。