作者:Ian Beavers

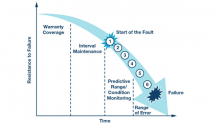

对于需要一系列同步模数转换器(ADC)的高速信号采样和处理应用,解偏斜和转换器的延迟变化匹配是至关重要的。围绕该特性展开的系统设计极为关键,因为从模拟采样点到处理模块之间的任何延迟失配都会使性能下降。对于交错式处理而言,样本对齐同样是必需的;在交错式处理时,一个转换器样本后紧跟另一个样本,且时间仅为一个时钟周期中的一小部分。

JESD204B第三代高速串行转换器接口的一个重要特性,是其能够确立系统中每个转换器的确定性延迟。正确理解并利用该特性,便可在单系统中针对多个ADC创建同步或交错采样系统。

由于确定性延迟是相对较新的转换器接口特性,系统设计人员经常就如何建立、目标信号以及如何部署为同步或交错式处理等方面存有诸多疑问。下文的部分常见问题与解答针对多个与FPGA一同采样的JESD204B转换器并使用确定性延迟进行系统设计而言。