作者:Mark Curtin和Paul O’Brien

本系列第一部分介绍了锁相环(PLL),说明了其基本架构和工作原理。另外举例说明了PLL在通信系统中的用途。在第二部分中,我们详细考察了相位噪声、参考杂散、输出漏电流等关键性能规格,还考虑了它们对系统性能的影响。在本部分中,我们将考察PLL频率合成器的主要构建模块。我们还将比较整数N和小数N架构。最后将总结市场上现有的VCO,同时列出ADI的现有频率合成器系列。

PLL频率合成器基本构建模块

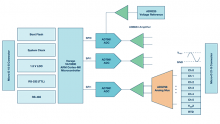

PLL频率合成器可以从多个基本构建模块的角度来考察。我们在前面已经提到过这个问题,下面将更加详细地进行探讨:

* 鉴频鉴相器(PFD)

* 参考计数器(R)

* 反馈计数器(N)

* 鉴频鉴相器(PFD)

频率合成器的核心是鉴相器,也称鉴频鉴相器。在鉴相器中,将比较参考频率信号与从VCO输出端反馈回来的信号,结果得到的误差信号用于驱动环路滤波器和VCO。在数字PLL (DPLL)中,鉴相器或鉴频鉴相器是一个逻辑元件。三种最常用的实现方法为:

* 异或(EXOR)栅极

* J-K触发器

* 数字鉴频鉴相器

这里,我们只考虑PFD,这也是ADF4110和ADF4210频率合成器系列中使用的元件,因为与EXOR栅极和J-K触发器不同,处于解锁状态时,其输出为频差以及两个输入间相差的函数。