作者:Justin Munson

范围

本应用笔记介绍ADI公司高速转换器组表征高速数模转换器(DAC)的性能时所用的测试方法。评估高速DAC时,应当参考本应用笔记和相应的器件数据手册。更多信息,请联系高速转换器组。

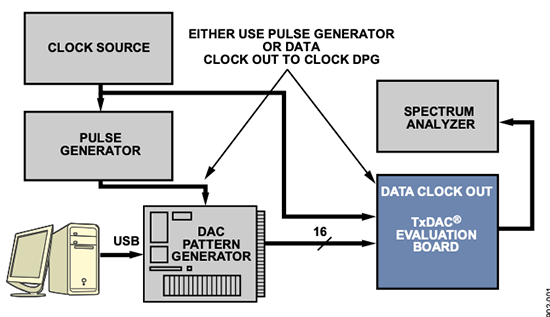

动态测试硬件设置

测试无杂散动态范围(SFDR)、交调失真(IMD)和噪声谱密度(NSD)等交流(AC)参数的典型硬件设置如图1所示。用于动态测试的基本设置包括DAC时钟的正弦源、低噪声电源、频谱分析仪和数据模式发生器。可以使用各种类型的模式发生器在DAC中驱动CMOS或LVDS数据,包括任意波形发生器(AWG)和现场可编程门阵列(FPGA)等。ADI公司也提供了一种数据模式发生器,以协助进行基准评估。

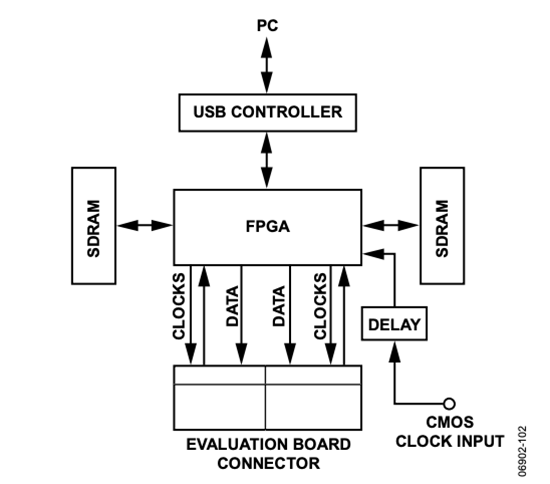

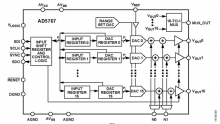

数据模式发生器2 (DPG2)

数据模式发生器2 (DPG2)旨在简化对ADI公司高速DAC产品的评估。DPG2的框图参见图2。DPG2提供双通道,每通道16位,支持LVDS和CMOS标准。LVDS模式下,每通道的最大采样速率为1.25 GSPS;CMOS模式下为250 MSPS。

DPG2提供最高512 MB的RAM,以便产生复杂波形。另外,采用HSC-DAC-DPG-CLKDIS板并配合每个DPG2使用一条Samtec HQCD-030-15.00-TED-TEU-1电缆,还可一次同步最多4个DPG2。