作者:Rob Reeder ADI公司

本文介绍最常见的外部噪声源以及它们如何影响高速信号链的总动态系统性能,另外给出了一些模拟和数字小技巧,可用来改善您下一款设计的信噪比(SNR)。

简介

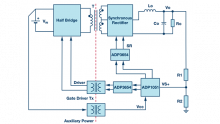

高速模拟信号链的设计可能非常具有挑战性,因为有如此多的噪声源需加以考虑。无论频率为高速(>10 MHz)或低速,转换器都应视为高速混频器,从而所有输入引脚——无论它们pin信号的类型如何(比如模拟、时钟或电源)——都能让这些pin脚的噪声引入到输出频谱。

转换器受限于工艺水平会有特定的底噪,其取决于内部节点和偏置。大部分情况下,高速ADC采用0.18 µCMOS设计,这意味着模拟电源(AVDD)为+1.8 V。这种趋势会持续扩大周边其它驱动模拟输入和时钟的支持器件极限,导致转换器产生偏压。

由于这一转换器裕量不断受限,每一款新的设计都会面临保持−150 dBFS/Hz或更低的极低噪声频谱密度的挑战。设计人员需认识到周边噪声贡献因素对整个信号链解决方案的重要性,而这就是这种认识至为重要的原因。诚然,有很多噪声原理。本指南涉及其中的两条原理:噪声带宽和噪声源叠加。

噪声带宽

噪声带宽不同于典型的放大器或滤波器截止点的−3 dB带宽。噪声波形具有不同的形状(矩形),表示带宽的总积分。这表示考虑噪声带宽贡献因素时,您需要略为调整噪声计算。

对于一阶系统而言——比如一阶低通滤波器——噪声带宽会宽57%。对于二阶系统,噪声带宽会宽22%;而三阶系统为15.5%,以此类推。在计算中纳入噪声带宽时,可快速参考表1。