探索不同的 SAR ADC 模拟输入架构

selina -- 周二, 11/21/2017 - 15:04

Ryan Curran 应用工程师, ADI公司

Ryan Curran 应用工程师, ADI公司

在所有器件特性中,噪声可能是一个特别具有挑战性、难以掌握的设计课题。这些挑战常常导致一些道听途说的设计规则,并且开发中要反复试错。本文将解决相位噪声问题,目标是通过量化分析来阐明如何围绕高速数模转换器中的相位噪声贡献进行设计。本文旨在获得一种"一次成功"的设计方法,即设计不多不少,刚好满足相位噪声要求。

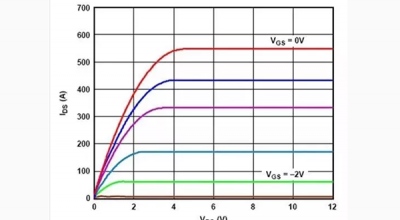

射频(RF)和微波放大器在特定偏置条件下可提供最佳性能。偏置点所确定的静态电流会影响线性度和效率等关健性能指标。虽然某些放大器是自偏置,但许多器件需要外部偏置并使用多个电源,这些电源的时序需要加以适当控制以使器件安全工作。

接下来,我们主要来说说偏置时序控制要求。

电源时序控制

简介

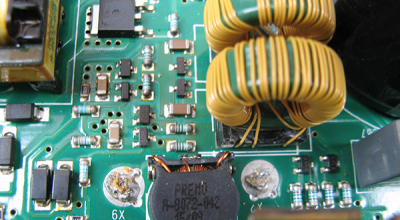

逐次逼近型模数转换器(因其逐次逼近型寄存器而称为SARADC)广泛运用于要求最高18 位分辨率和最高5 MSPS 速率的应用中。其优势包括尺寸小、功耗低、无流水线延迟和易用。

Maithil Pachchigar ADI公司

简介

在很多应用中,模拟前端接收单端或差分信号,并执行所需的增益或衰减、抗混叠滤波及电平转换,之后在满量程电平下驱动ADC输入端。本文探讨精密数据采集信号链的噪声分析,并深入研究这种信号链的总噪声贡献。

Σ-Δ概述

Rob Reeder 系统应用工程师 ADI公司

Doug Ito ADI公司产品应用工程师

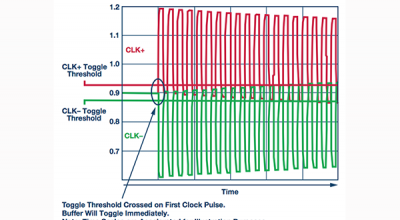

根据定义,高速模数转换器(ADC)是对模拟信号进行采样的器件,因此必定有采样时钟输入。某些使用ADC的系统设计师观测到,从初始施加采样时钟的时间算起,启动要比预期慢。出人意料的是,造成此延迟的原因常常是外部施加的ADC采样时钟的启动极性错误。

Derrick Hartmann 应用工程师 ADI公司

作者:Tim Watkins,核心应用部门,ADI公司

内容提要